|

元件类型Net Tie可以让PCB工程师和设计师更加灵活得处理各种设计挑战。本文探讨了在Altium Designer中使用Net Tie在PCB的特定位置将一个短接的单独网络连接成多个网络的优势。

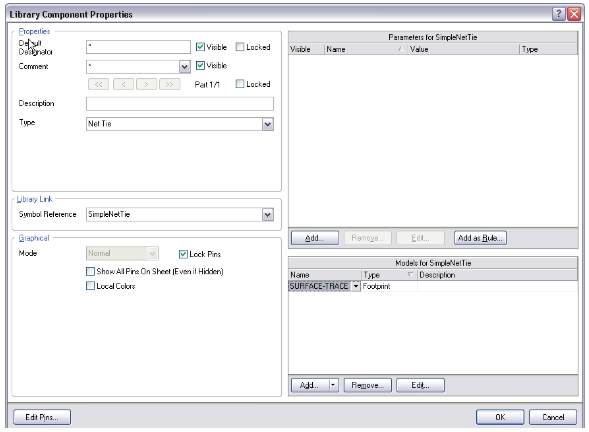

什么是Net Tie以及如何使用 定义一个Net Tie元件只需在“Component Properties”对话框的“Type”字段中指定它即可。

图1:Net Tie元件的Component Properties对话框

Net Tie有两种设计类型:Net Tie和Net Ties(In BOM)。每种类型都可以在Component Properties对话框的“Type”字段的下拉选项中选择。当使用Net Tie时,元件的原理图符号会附加到一个特定类型的封装,该封装的焊盘连接(短路)在一起。原理图符号的引脚和PCB封装焊盘之间的网络连接是按常规方式建立的;但是,在物料清单(BOM)中,不会显示该元件。使用Net Ties(In BOM)可以在BOM中显示出来。这两种类型都将在本文中进行探讨。

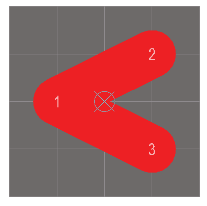

Net Tie最简单的一种形式是两个引脚组件,连接到一个带两个焊盘的封装,其中焊盘之间连接在一起。

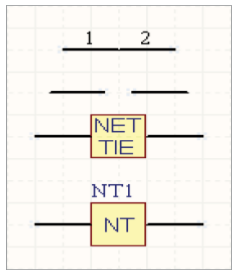

与其他原理图符号类型一样,符号引脚designator和名称的显示是可选的,引脚之间的原理图布线确定网络连接,并且原理图和PCB之间建立了引脚到焊盘的连接。 Net Tie组件的图形是任意的,在某些情况下是不必要的。例如,两针Net Tie组件可以表示为看起来像原理图中的一根线(完全隐藏了它的存在)。

图2:两个引脚Net Tie原理图符号示例。

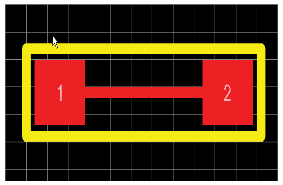

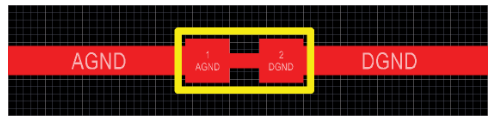

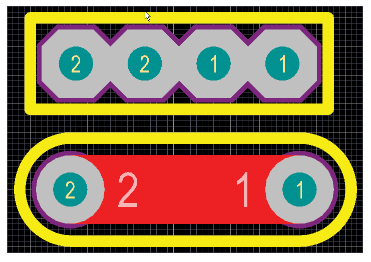

图3:Net Tie封装,可以用于短接两个不同网络名的敷铜。

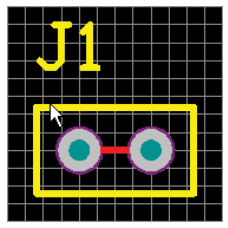

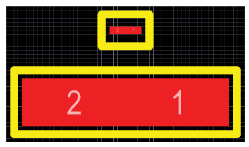

该元件将在BOM表中显示为一个排针元件。 该短路的连接线可以后期去除,以实现可选的短路跳线。

图4:Net Ties(In BOM),用于指定两个引脚的排针。

在布线到Net Tie封装的焊盘时,设计规则检查(DRC)允许将与每个焊盘相关的网络布线到其他相同的网络,而无需显示违规情况,从而允许连接(短路)焊盘到两个不同的网络。

如果不同网络之间两条布线的末端在封装中短路在一起,则DRC将标记违规。这是由于在Net Tie封装限制之外的两个不同网络之间产生了短路。

两个不同网络的走线,违反规则

图5:可以设置Net Tie允许使用不同宽度的走线将两个不同的网络一起布线。

图6:可以创建Net Tie元件,通过合并通孔焊盘来允许在各个布线层之间进行布线。

图7:可以创建Net Tie封装,以允许不同网络之间短路,然后可以移除短路铜。

Net Tie元件允许在PCB的Net Tie封装的位置处在两个不同的网络之间建立连接。 DRC将标记设计中其他地方这些不同网络之间的任何其他短路违规情况。

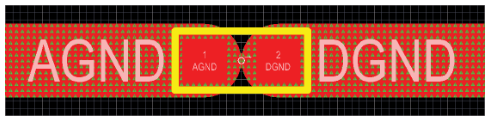

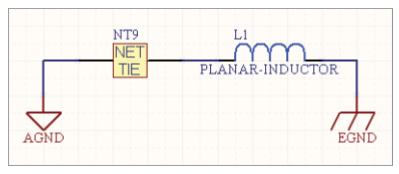

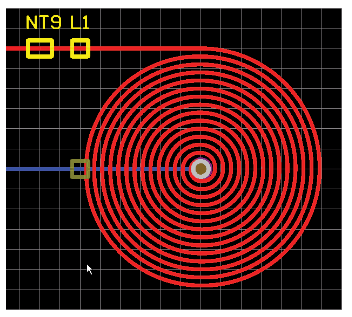

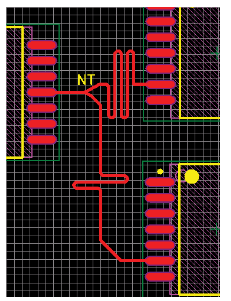

平面电感器对电路板布局提出了特殊的挑战。当电感器的各种绕组直接放置在印刷电路板上时,每个绕组都由形成各种电感器线圈的走线轨迹组成。每个线圈是一个连续的敷铜,在绕组的两端各有不同的网。电感器绕组走线通常会在绕组两端的每个网络之间引入短路,从而导致违反DRC规则。

您可以使用Altium Designer PCB设计软件来将Net Tie元件与电感器绕组串联放置。这提供了一种连接不同网络的方法,其中一个网络表示绕组和电路的一侧,另一个网络表示第二个电气连接。

图8:将两个不同的接地平面网与平面电感器绕组桥接的电路。 Net Tie组件提供了一种将AGND连接到EGND网络的方法,EGND网络遍布整个平面绕组。

在这个例子中,丝印和参考标号已经显示出来,以说明组件在电路板布局中的位置。但是,这些特征可能会在实际设计中遗漏,从而加剧了高密度设计中的混乱和混乱。

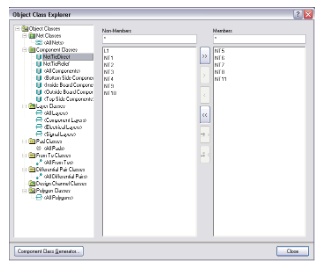

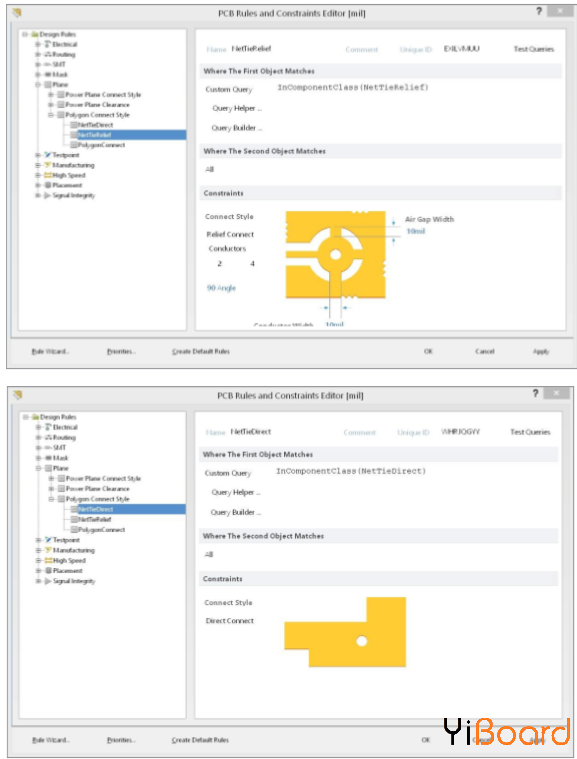

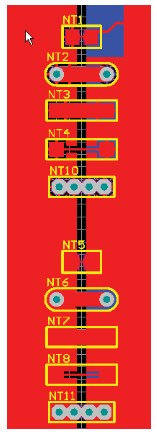

这里的网络NT5、NT6、NT7、NT8和NT 11已放置在标记为NetTieDirect的组件类中。

图9:Net Tie元件可用于连接不同网络的多边形,以允许仅在一个位置短路。这两个网络之间的其他短路将由DRC在整个电路板上标记为违反规则。

图10:在上面的示例中,已在PCB上放置了多个Net Tie组件,以说明如何确定设计规则的范围以指定多边形连接样式,以实现所需的结果。

图11:已经为示例NetTieDirect和NetTieRelief创建了两个Polygon Connect样式规则,它们分别作用于组件类NetTieDirect和NetTieRelief。

图12:在PCB的上部区域,按照花式连接规则将网络连接线连接到敷铜。

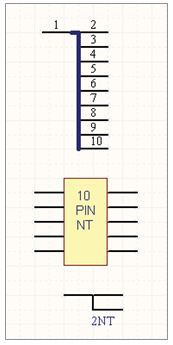

图13:多引脚Net Tie示意图符号示例。

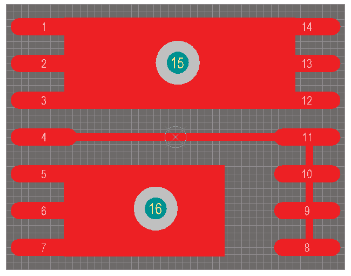

图14:使用Net Tie封装可以实现的示例。

电路板的下部遵循直接连接样式。请注意,根据间隙规则,敷铜连接铜的方法。

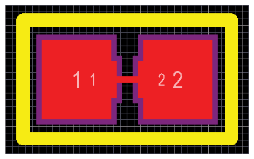

Net Tie可以具有无限数量的电连接无限数量的网络的引脚和焊盘。

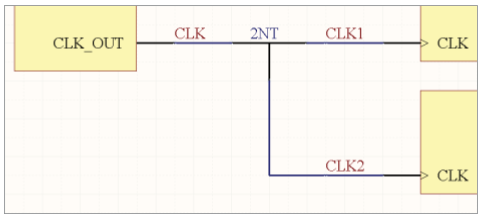

当对时间要求严格的信号的信号路径必须同时在合理的增量内到达网络的负载端时,网络长度调整提出了一个有趣的挑战。在下面的示例中,生成了时钟信号并将其路由到两个不同的IC封装。至关重要的是,该高速信号的信号路径必须在合理的公差范围内达到相同的长度。

多个网络Net Tie的使用可将网络分解为单独的网络,以进行长度调整。相关的封装允许同一信号传播不同的网络路径。

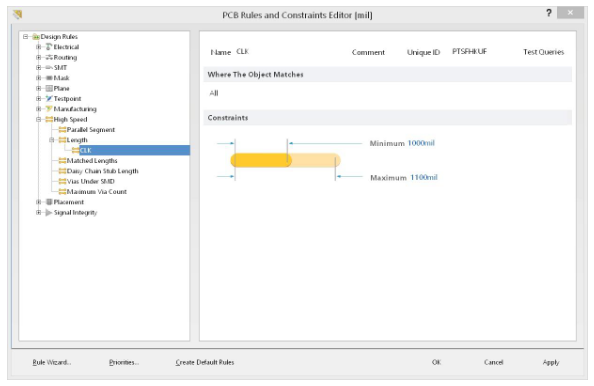

网络CK1和CK2被关联到标记为CLK的网络类别中,然后为该类别创建一个长度规则。

一旦网络CK1和CK2布线,就可以将其长度调整为“长度”规则,该规则指定了总长度和公差。

封装允许同一信号传播不同的网络路径

网络CK1和CK2已关联

CK1和CK2已布线,可以将其长度调整为“Length”规则

总结 Net Tie是一种独特的元件类型,它使电子工程师和PCB设计人员可以灵活地将不同的网络短路在一起。 按照上述步骤进行操作,Altium Designer可以帮助您解决在设计印刷电路板时的设计要求挑战。

本文翻译自:https://resources.altium.com/p/using-net-ties-to-meet-pcb-design-requirements,如有错漏,敬请指正。 |