|

PSoC 6 Wi-Fi BT原型开发套件(CY8CPROTO-062-4343W)是便宜的PSoC 6开发的入门版本。该开发套件的其中一项功能带有两个间距为40 mm的PDM麦克风,用于立体声的音频采样。这些样本是通过PDM-PCM Converter外设获得的,在本篇文章中,该外设将配置为采集44.1 kHz标准速率(与音频CD相同的速率)的样本。

ModusToolbox是PSoC 6系列的首选开发环境,它包括PSoC 6 SDK和ModusToolbox IDE,后者本身包括用于硬件和某些中间件的多个配置器。主要配置器(即设备配置器Device Configurator)大大减少了配置设备的系统功能和外围设备所需的工作。开发人员可以使用图形界面来设置其配置参数,如果在生成C代码之前存在任何无效参数,该工具将发出警告/错误。当然,这并不意味着开发人员不需要任何工作。设备配置器还远远不够完美,除了最基本的外设之外,很可能必须参考《架构技术参考手册》(TRM)。在下面的文章中将对两项要点进行演示。

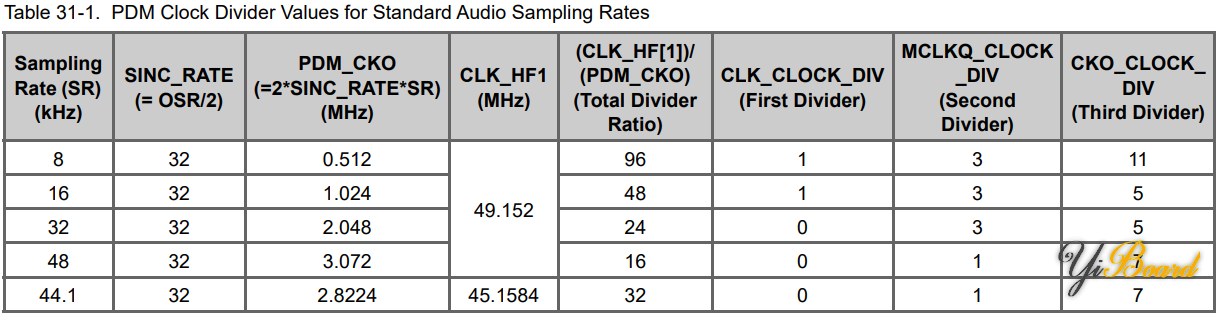

配置PDM-PCM外围设备 让我们从最简单的步骤开始。 TRM中的表31-1提供了有关如何针对几种标准采样率(fs)配置PDM-PCM Converter的时序参数的示例。

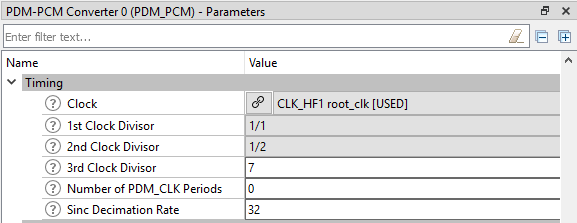

要将fs = 44.1 kHz的值输入Device Configurator,请在ModusToolbox IDE中双击项目的design.modus文件。在“ Peripherals”选项卡中,展开“ Digital”资源,然后选择“ PDM-PCM Converter 0”。在“Parameters”窗口中,向下滚动至“Timing”参数,然后输入值,如图1所示。请注意,TRM表31-1中存在一个错误。 fs = 44.1 kHz的总除数比应为16,而不是32。这不会对配置产生影响,因为我们没有将此值直接输入到Device Configurator中,但仍可能造成混淆。

图1:PDM-PCM Converter的时序参数

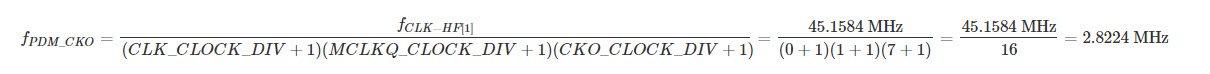

这三个时钟分频器将生成PDM_CKO时钟信号,该信号用于为外部PDM麦克风计时,如下所示:

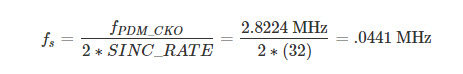

然后,SINC_RATE根据以下公式确定fs:

尽管在本文中未涉及,但还需要为PDM-PCM Converter设置其他几个参数,包括通道设置、滤波器首选项和中断触发器。有关这些属性的更多信息,请参考TRM。

配置外设时钟 以下是比较复杂的部分。我们如何获得fCLK-HF [1] = 45.1584 MHz? TRM的第31.2.3节介绍了将外部晶体振荡器(ECO)与锁相环(PLL)结合在一起作为一种解决方案,我发现这种方法很好用。要修改CLK-HF1时钟的配置,请单击Clock参数的链接图标(图2)。

图2:跳转到链接时钟信号的配置

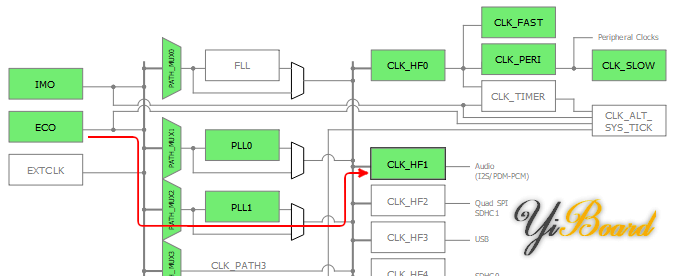

然后打开“Platform”选项卡,除其他外,该选项卡使您可以配置系统时钟。该选项卡的中心应是一个交互式时钟图,该时钟图指示启用了哪些时钟元素以及它们如何相互连接。遵循TRM的示例,我们希望如图3所示进行内部连接。

图3:突出显示所需元件连接的时钟图

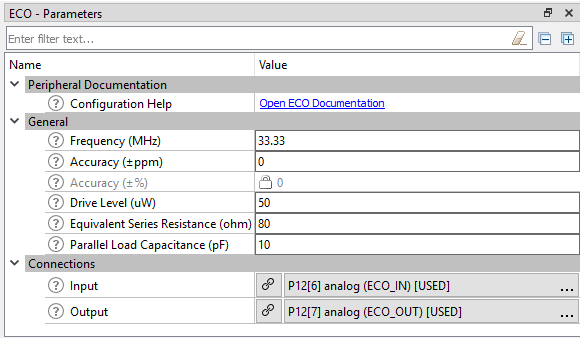

我们将从路径的开头开始并配置ECO。如果ECO框不是绿色,请在时钟图中双击它以将其启用。请注意,“Parameters”窗口现在具有几个可供我们更改的参数。这些是开发板上外部晶体的特性,在CY8CPROTO-062-4343W上,外部晶振是TXC的34.4064 MHz晶体。TXC 8Y系列数据表为我们提供了配置ECO外设所需的所有信息。但是,如果尝试从“'Frequency (MHz)”字段中输入34.4064开始,则会收到以下警告: Unable to evaluate parameter 'Frequency (MHz)' on personality 'ECO'. '34.41' is not within the legal range of [4.00-33.33] for parameter 'Frequency (MHz)'

这不是致命错误,因为如果输入33.33而不是34.41,外围设备仍然可以正常工作,但是由于我们很快就会看到的原因,这很烦人。输入此值和其他值后,ECO配置应如图4所示。

图4:最终的ECO配置

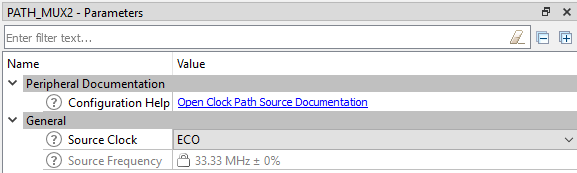

路径中的下一个是PATH_MUX2多路复用器。在时钟图中单击此元素可查看其参数。选择“ ECO”作为Source Clock值(图5)。

图5:最终的PATH_MUX2配置

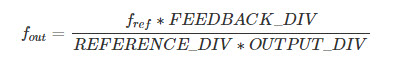

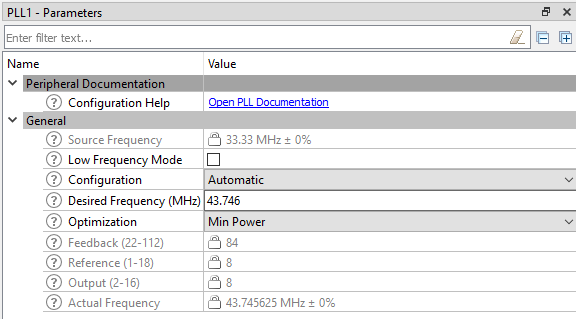

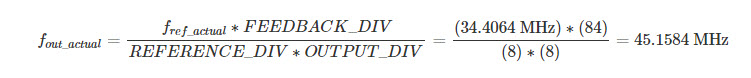

接下来,单击时钟图中的PLL1元素以填充“ Parameters”窗口。这就是输入33.33 MHz ECO频率的结果。请注意,“Source Frequency”将自动填充为33.33 MHz。这就是设备配置器所认为的PLL参考时钟频率(fref)。配置器将执行以下计算以确定PLL的输出频率(显示在“Actual Frequency”字段中):

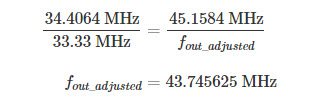

默认情况下,Configuration参数设置为“Automatic”,这意味着我们可以输入所需的输出频率,并且设备配置器将确定满足上述公式的最佳分频器值集。但是,我们必须记住,它将以33.33 MHz的fref值而不是34.4064 MHz的实际fref值执行该计算。因此,我们不能在“Desired Frequency(MHz)”字段中输入45.1584,而必须使用如下计算的调整后的值:

在“Desired Frequency(MHz)”字段中输入“ 43.745625”,得到的配置如图6所示。

图6:最终的PLL1配置。

然后,我们可以使用fref的实际值来确保使用此配置将获得正确的输出。

因此,尽管“Actual Frequency”字段显示为43.745625 MHz,但实际上是我们期望的45.1584 MHz。

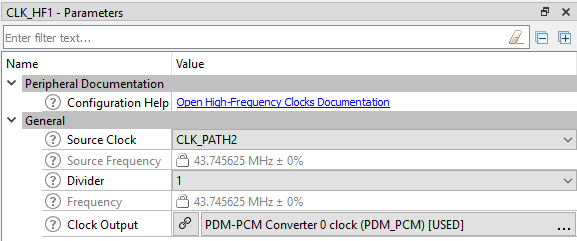

最后,在时钟图中单击CLK_HF1元素。将Source Clock值更改为“CLK_PATH2”,如下图7所示。

图7:最终的CLK_HF1配置

选择File > Save以保存您的配置,然后生成源代码。 |